指令集架构

目录

指令集架构

在计算机科学中,一个指令集架构(ISA),也被称为计算机体系结构,是一个抽象的模型一的计算机。执行由该ISA描述的指令的设备,例如中央处理单元(CPU),称为实现。

一般而言,指令集架构定义了支持的指令、数据类型、寄存器、管理主内存的硬件支持、基本特性(例如内存一致性、寻址模式、虚拟内存)以及一系列实现的输入/输出模型。

指令集架构以不依赖于该实现的特征的方式指定在该ISA的实现上运行的机器代码的行为,提供实现之间的二进制兼容性。这使得ISA的多种实现在性能、物理大小和货币成本(除其他外)等特征上不同,但能够运行相同的机器代码,因此性能较低、成本较低的机器可以更换成本更高、性能更高的机器,而无需更换软件。它还支持微架构的演进ISA的实现,以便ISA的更新、更高性能的实现可以运行在前几代实现上运行的软件。

如果操作系统为特定指令集架构维护了标准且兼容的应用程序二进制接口(ABI),则机器代码将在该ISA和操作系统的未来实现上运行。但是,如果一个ISA支持运行多个操作系统,它并不能保证一个操作系统的机器代码会在另一个操作系统上运行,除非xxx个操作系统支持运行为另一个操作系统构建的机器代码。

可以通过添加指令或其他功能,或添加对更大地址和数据值的支持来扩展ISA;扩展ISA的实现仍然能够为没有这些扩展的ISA版本执行机器代码。使用这些扩展的机器代码只会在支持这些扩展的实现上运行。

它们提供的二进制兼容性使ISA成为计算中最基本的抽象之一。

指令集架构的分类

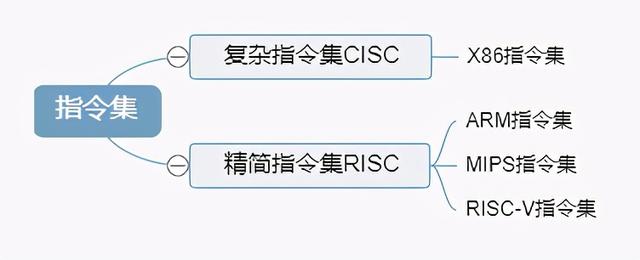

指令集架构可以按多种不同方式分类。一个常见的分类是按体系结构的复杂性。一个复杂指令集计算机(CISC)有许多专门的说明,其中一些可能只在实际程序中很少使用。甲精简指令集计算机(RISC)通过有效地实现仅是经常在程序中使用的指令,而较不常见的操作被作为子程序来实现,其具有产生的额外处理器的执行时间通过很少使用偏移简化了处理器。

其他类型包括超长指令字(VLIW)架构,以及密切相关的长指令字(LIW)和显式并行指令计算(EPIC)架构。这些架构通过让编译器负责指令发布和调度,以比RISC和CISC更少的硬件来开发指令级并行性。

已经研究了更复杂的体系结构,例如最小指令集计算机(MISC)和一个指令集计算机(OISC)。这些是理论上重要的类型,但尚未商业化。

指令集架构说明

机器语言是由离散的语句或指令构成的。在处理架构上,给定指令可以指定:

- 操作码(要执行的指令)例如添加、复制、测试

- 任何显式操作数:

寄存器文字/常量值用于访问内存的寻址模式

更复杂的操作是通过组合这些简单的指令来构建的,这些指令是按顺序执行的,或者按照控制流指令的其他方式执行。

指令集架构设计

指令集的设计是一个复杂的问题。微处理器的历史有两个阶段。xxx个是CISC(复杂指令集计算机),它有许多不同的指令。然而,在1970年代,IBM等地方做了研究,发现集合中的许多指令都可以消除。结果是RISC(精简指令集计算机),一种使用较小指令集的架构。更简单的指令集可以提供更高速度、减小处理器尺寸和降低功耗的潜力。但是,更复杂的集合可能会优化常见操作,提高内存和缓存效率,或者简化编程。

一些指令集设计者为某种系统调用或软件中断保留一个或多个操作码。例如,MOSTechnology6502使用00H,ZilogZ80使用八个代码C7,CF,D7,DF,E7,EF,F7,FFH而Motorola68000使用A000..AFFFH范围内的代码。

如果指令集满足Popek和Goldberg虚拟化要求,则快速虚拟机更容易实现。

如果将内存的“未编程”状态解释为NOP,则在免疫感知编程中使用的NOP幻灯片更容易实现。

在具有多个处理器的系统,无阻塞同步算法是实现容易得多如果该指令集包括用于一些诸如“支持读取和加载”,“负载链路/条件存储”(LL/SC)或“原子比较和交换”。

指令集实现

任何给定的指令集都可以通过多种方式实现。实现特定指令集的所有方式都提供相同的编程模型,并且该指令集的所有实现都能够运行相同的可执行文件。实现指令集的各种方式会在成本、性能、功耗、大小等之间做出不同的权衡。

在设计处理器的微架构时,工程师使用“硬连线”电子电路块(通常单独设计),例如加法器、多路复用器、计数器、寄存器、ALU等。然后通常使用某种寄存器传输语言来描述使用这种物理微架构对ISA的每条指令进行解码和排序。有两种基本方法可以构建控制单元来实现此描述(尽管许多设计使用中间方法或折衷方法):

- 一些计算机设计“硬连线”完整的指令集解码和排序(就像微体系结构的其余部分一样)。

- 其他设计采用微代码例程或表格(或两者)来执行此操作——通常作为片上ROM或PLA或两者兼而有之(尽管历史上曾使用单独的RAM和ROM)。在西数MCP-1600是一个老例如,使用微码专用,单独的ROM。

一些设计将硬连线设计和微代码结合用于控制单元。

一些CPU设计使用可写控制存储——它们将指令集编译到CPU内的可写RAM或闪存(例如Rekursiv处理器和ImsysCjip)、或FPGA(可重构计算)。

ISA也可以由解释器在软件中模拟。自然地,由于解释开销,这比在仿真硬件上直接运行程序要慢,除非运行仿真器的硬件快一个数量级。今天,新ISA或微体系结构的供应商通常会在硬件实现准备就绪之前向软件开发人员提供软件模拟器。

通常,实现的细节对为指令集选择的特定指令有很大的影响。例如,指令流水线的许多实现只允许每条指令进行单个内存加载或内存存储,从而导致加载-存储架构(RISC)。再比如,一些早期的指令流水线实现方式导致了延迟槽。

高速数字信号处理的需求已经推向相反的方向——迫使指令以特定方式执行。例如,为了足够快地执行数字滤波器,典型的数字信号处理器(DSP)中的MAC指令必须使用一种可以同时获取一条指令和两个数据字的哈佛架构,并且需要一个单周期的乘法累加乘数。