忆阻器

目录

什么是忆阻器

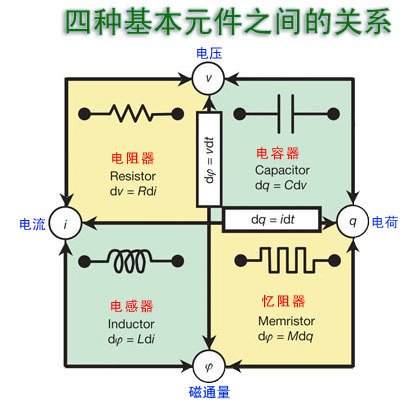

忆阻器,是一种非线性二端子电部件与电荷和磁性的磁链。它于1971年由LeonChua描述和命名,完成了基本电气元件的理论四重奏,其中还包括电阻器、电容器和电感器。

Chua和Kang后来将这个概念推广到忆阻系统。这样的系统包括一个电路,该电路由多个常规组件组成,该电路模拟了理想忆阻器组件的关键特性,并且通常也被称为忆阻器。已经开发了几种这样的忆阻器系统技术,特别是ReRAM。

电子设备中忆阻特性的识别引起了争议。在实验上,理想的忆阻器还有待证明。

建模和验证

工程师和科学家很少以原始形式分析物理系统。相反,他们构建了一个近似系统行为的模型。通过分析模型的行为,他们希望预测实际系统的行为。构建模型的主要原因是物理系统通常太复杂而无法进行实际分析。

在20世纪,研究人员在无法识别忆阻特性的设备上进行了工作。这提出了应将此类设备识别为忆阻器的建议。Pershin和DiVentra提出了一种测试,可以帮助解决一些长期存在的关于理想忆阻器是否确实存在或纯粹是数学概念的争论。

忆阻器的实现

潜在应用

忆阻器仍然是实验室的好奇心,因为其数量还不足以获得任何商业应用。尽管缺乏大规模供应,根据AlliedMarketResearch的数据,忆阻器市场在2015年价值320万美元,到2022年将价值7900万美元。

忆阻器的一个潜在应用是用于超导量子计算机的模拟存储器。

忆阻器有可能被塑造成非易失性固态存储器,它可以允许比访问时间类似于DRAM的硬盘驱动器更高的数据密度,从而取代这两个组件。惠普设计了一个交叉锁存存储器的原型,该存储器可以在一平方厘米内容纳100吉比特,并提出了一种可扩展的3D设计(由多达1000层或每厘米31拍比特组成)。2008年5月,惠普报告说,其设备目前的速度约为DRAM的十分之一。设备的电阻将用交流电读取这样存储的值就不会受到影响。2012年5月,据报道,访问时间已提高到90纳秒,比同时代的闪存快近一百倍。同时,能耗仅为闪存的百分之一。

忆阻器在可编程逻辑、信号处理、超分辨率成像、物理神经网络、控制系统、可重构计算、脑机接口、中的应用]和RFID。忆阻器件可能用于有状态的逻辑隐含,允许替代基于CMOS的逻辑计算。在这个方向上已经报道了一些早期的工作。

2009年,一个由LC网络和忆阻器组成的简单电子电路用于模拟单细胞生物适应性行为的实验。研究表明,受到一系列周期性脉冲的影响,电路学习并预测下一个脉冲,类似于粘菌Physarumpolycephalum的行为,其中细胞质中通道的粘度响应周期性环境变化。这种电路的应用可以包括,例如,模式识别。该DARPA突触项目资助的惠普实验室,在合作与波士顿大学NeuromorphicsLab一直在开发可能基于忆阻系统的神经形态架构。2010年,范思哲和钱德勒描述了MoNETA(模块化神经探索旅行代理)模型。MoNETA是xxx个实现全脑电路的大规模神经网络模型,使用忆阻硬件为虚拟和机器人代理提供动力。Merrikh-Bayat和Shouraki演示了忆阻器交叉结构在模拟软计算系统构建中的应用。2011年,他们展示了如何将忆阻器交叉开关与模糊逻辑结合以创建模拟忆阻神经模糊具有模糊输入和输出终端的计算系统。学习是基于受Hebbian学习规则启发而创建的模糊关系。

2013年,LeonChua发表了一篇教程,强调了忆阻器所涵盖的复杂现象和应用的广泛范围,以及它们如何用作非易失性模拟存储器并可以模仿经典的习惯和学习现象。